## КАТАЛОГ ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ

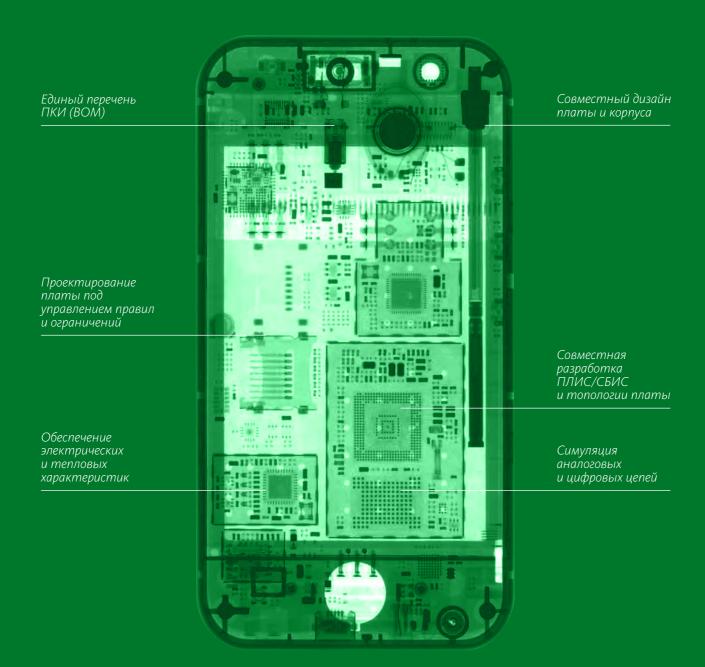

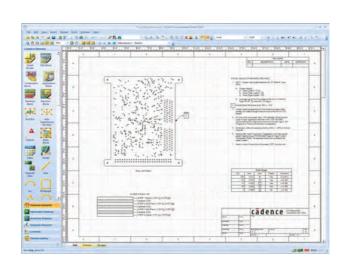

САПР печатных плат верхнего уровня Cadence® Allegro®

САПР печатных плат Cadence® OrCAD®

Система моделирования печатных плат Cadence® Sigrity™

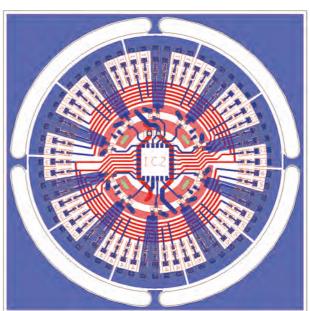

Печатные платы iPhone разработаны в САПР Cadence Allegro

## Оглавление

Варианты поставки / С 52

| РСВ SOFT. поставка САПР печатных плат с 2011 года / С 4                   |

|---------------------------------------------------------------------------|

| Маршрут проектирования печатных плат Cadence Allegro / Sigrity / C 6      |

| Почему разработчики выбирают Cadence Allegro / С 8                        |

| Конфигурация рабочих мест для проектирования ПП /С 10                     |

| Функционал базовой лицензии и дополнительных опций Cadence Allegro / С 12 |

| Опция трассировки скоростных плат – High Speed Option / С 15              |

| Опция оптимизации выводов ПЛИС – FPGA System Planner / С 16               |

| Опция проектирования СВЧ-плат – Analog/RF Option / С 17                   |

| Новые возможности версии Cadence Allegro 17.2-2016 <b>/ С 18</b>          |

| САПР печатных плат OrCAD (основан на технологиях Allegro) /С22            |

| Продукты OrCAD и Allegro /С24                                             |

| Набор функций OrCAD и Allegro /С26                                        |

| Система схемного моделирования OrCAD PSpice Designer / C 30               |

| Анализ целостности сигналов OrCAD PCB SI / C 31                           |

| Мастер создания компонентов OrCAD Library Builder / С 32                  |

| Система управления данными Engineering Data Management (EDM) / С 33       |

| Оформление КД по ГОСТ OrCAD Documentation Editor / С34                    |

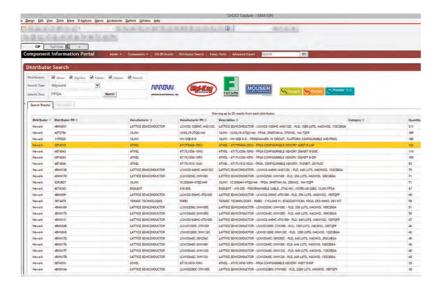

| Единая база компонентов Component Information Portal (CIP) / С 35         |

| Технологические проверки OrCAD DFM Checker / C 36                         |

| Электрические проверки OrCAD Sigrity ERC / С37                            |

| Набор утилит OrCAD PCB Productivity Toolbox / С 38                        |

| Оптимизация трассировки ПЛИС OrCAD FPGA System Planner / С 39             |

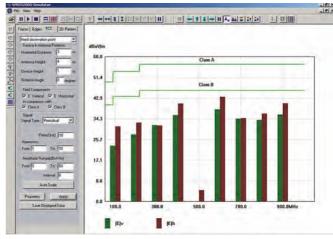

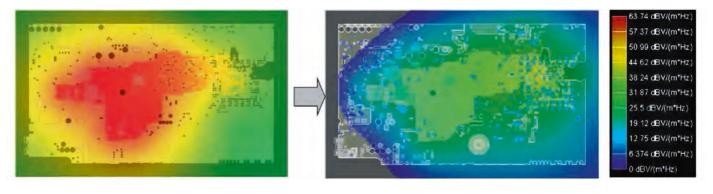

| Sigrity. Электромагнитное и тепловое моделирование <b>/С40</b>            |

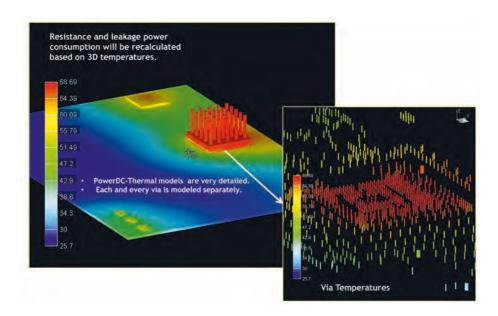

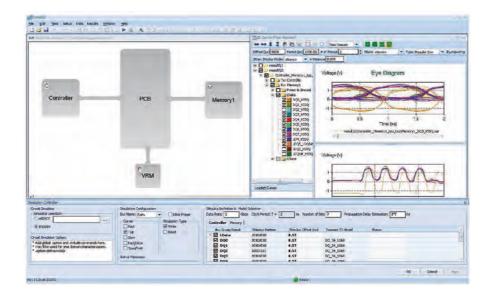

| Температурно-электрическая симуляция – Sigrity PowerDC / C 42             |

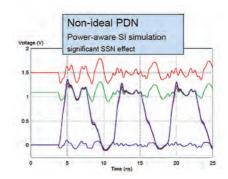

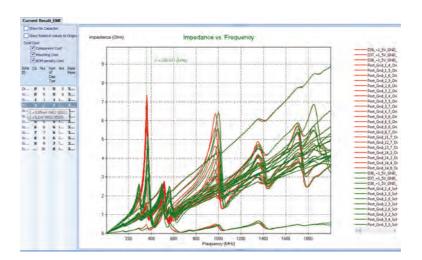

| Целостность сигналов, питаний и ЭМС – Sigrity PowerSI / С 44              |

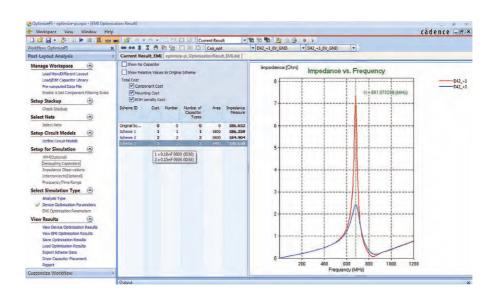

| Оптимизация матрицы конденсаторов – Sigrity OptimizePI / C 45             |

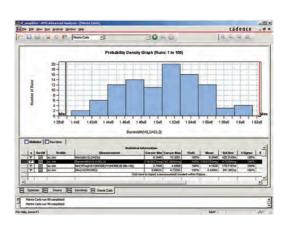

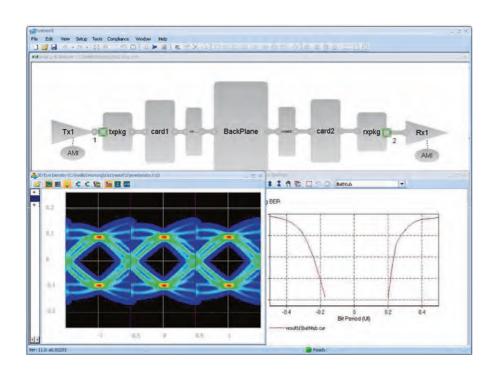

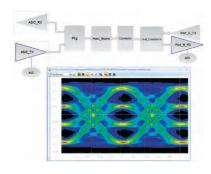

| Пред- и пост-топологический анализ – Sigrity SystemSI / C 46              |

| Что нового в Sigrity-2017 <b>/ С 48</b>                                   |

| Варианты лицензий и состав пакетов Sigrity <b>/ С 49</b>                  |

| Спецпредложения на САПР Cadence в 2017 году <b>/ С 50</b>                 |

# РСВ SOFT ПОСТАВКА САПР ПЕЧАТНЫХ ПЛАТ С 2011 ГОДА

Компания PCB SOFT является эксклюзивным официальным дистрибьютором Cadence Design Systems в России и Беларуси и поставляет систему автоматизированного проектирования печатных плат Allegro, OrCAD и систему электромагнитного 3D моделирования Sigrity.

В 2015 и 2016 годах Cadence Design Systems удостоила компанию PCB SOFT наградами за особые достижения в продаже CAПР и поддержке пользователей.

#### **ВНЕДРЕНИЕ**

Компания PCB SOFT обеспечивает полноценное внедрение сквозного маршрута проектирования, осуществляет интеграцию с другими САПР и PDM/PLM системами.

#### **ТРЕНИНГИ**

Учебный класс PCB SOFT в Москве регулярно проводит тренинги инженеровконструкторов по освоению методологии проектирования и моделирования сложных многослойных печатных плат в САПР печатных плат **Allegro** и **Sigrity**. Также возможно проведение выездных семинаров и обучение специалистов на базе предприятия-заказчика.

#### Обучение

В сотрудничестве с МГТУ им.Баумана в Москве организован учебный центр, регулярно проводящий обучение инженеров-конструкторов методологии проектирования сложных многослойных печатных плат в САПР ПП Cadence Allegro, с предоставлением документов о повышении квалификации.

#### СЕРТИФИКАЦИЯ

Специалисты компании PCB SOFT прошли сертификацию Cadence Design Systems и IPC.

# Маршрут проектирования печатных плат Cadence Allegro / Sigrity

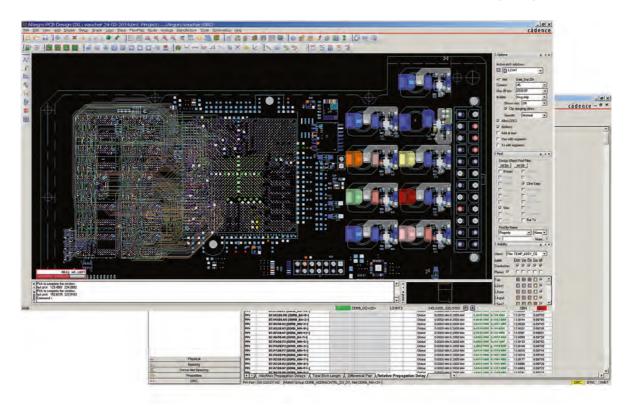

# САПР Cadence Allegro является лидирующей в мире системой для проектирования сложных многослойных печатных плат.

Это обусловлено сочетанием трех факторов:

- Allegro позволяет проектировать печатные платы высочайшей сложности, с возможностью применения всех современных технологий

- Работа инженеров-конструкторов в Allegro крайне эффективна, а обеспечение правил по технологичности и целостности сигналов выстроено оптимально

- Сроки внедрения Allegro предельно коротки, обучение инженеров можно выполнить за считанные недели, что обеспечивает быстрый возврат инвестиций

#### ПРЕИМУЩЕСТВА ДЛЯ ЗАКАЗЧИКОВ

Внедрение уникальных технологий Cadence повышает конкурентоспособность и эффективность российских предприятий на внутреннем и на мировом рынке.

#### При этом:

- Сроки разработки электроники сокращаются в 2-3 раза

- Затраты на разработку снижаются в 1.5-2 раза

- Количество ошибок при проектировании плат сокращается на 30-40%

- Снижается до 1-2 количество итераций, требуемых до запуска прибора в серию

- Сокращается на 20-30% число извещений об изменениях

- Существенно улучшается качество и внешний вид печатных плат

- Появляется возможность разработки инновационных продуктов на новом уровне

- Растет репутация предприятия в глазах зарубежных партнеров

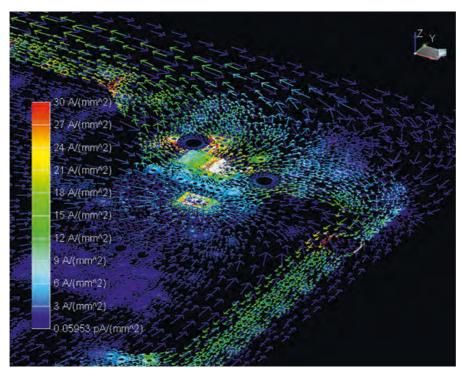

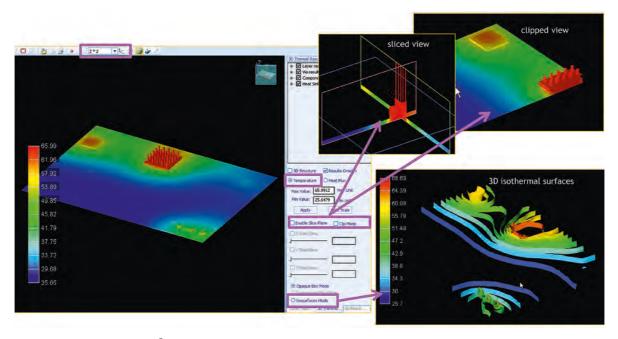

#### Система моделирования Cadence Sigrity

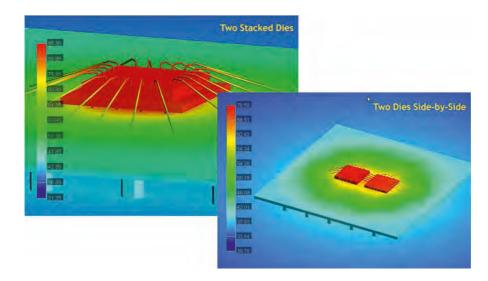

Система моделирования Sigrity – лучшее в своем классе решение для моделирования целостности сигналов с учетом питаний и ЭМС.

- Инструменты симуляции целостности питаний Sigrity содержат все необходимое для анализа как по постоянному, так и по переменному току, в том числе в 3D.

- Программное обеспечение для теплового анализа учитывает все необходимые факторы для точного расчета по теплу.

- Удобный интерфейс и мощный инструментарий позволяют разработчику оперативно выбрать номиналы и расположение конденсаторов, оптимизировать конфигурацию полигонов, подобрать параметры радиаторов.

Sigrity позволяет разработчикам еще до производства образцов обеспечить и подтвердить работоспособность вашего прибора в заданных условиях.

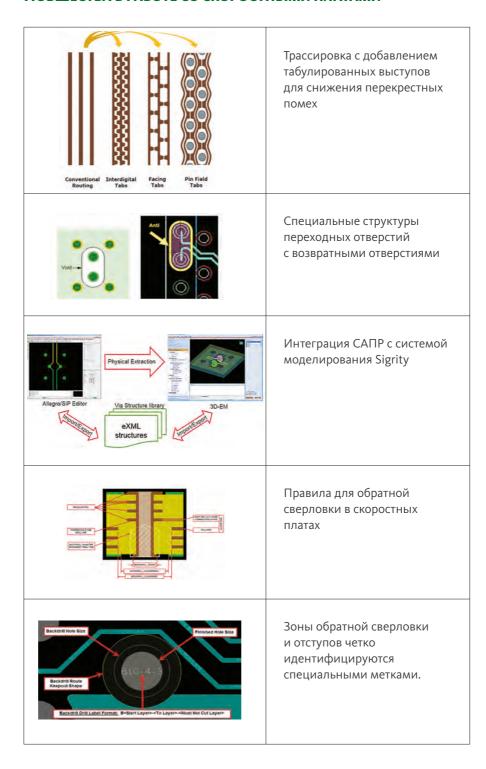

#### Пользователи САПР печатных плат Cadence Allegro

Маршрут проектирования на базе программного обеспечения Cadence освоили и успешно используют ведущие предприятия российской радиоэлектронной, военной и аэрокосмической отраслей и многие другие государственные и частные предприятия.

Масштабируемость САПР от недорогого OrCAD до продвинутых плавающих опций Allegro позволяет предприятиям получить оптимальную среднюю стоимость рабочего места и максимальную отдачу. Пред- и пост-топологическое моделирование в Sigrity позволяет в разы сократить время и стоимость разработки и изготовления опытных образцов, сделав изделие более технологичным и инновационным.

# Почему разработчики выбирают Cadence Allegro

Удобный интерфейс редактора схем

Интерактивная связь между редакторами схем и печатных плат

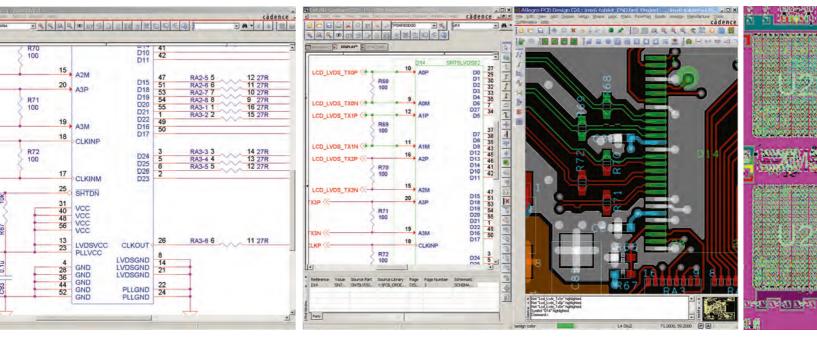

Схемный редактор, совместимый с OrCAD, и возможность качественного импорта схем, плат и библиотек из P-CAD, вкупе с простым и *дружественным интерфейсом*, делают Cadence Allegro наилучшим вариантом для постепенного «бесшовного» перехода на новые технологии. Встроенные в Allegro отчеты дают возможность вывода КД по ЕСКД прямо из САПР.

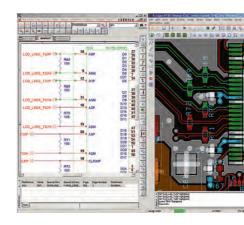

Удобная связь между схемным редактором и редактором печатных плат позволяет вам «перетащить» компонент со схемы на плату при размещении, выделить компонент на схеме и увидеть его на плате, выделить вывод или цепь на плате и увидеть его на схеме. Функционал единой библиотеки компонентов предприятия снижает число ошибок, связанных с человеческим фактором.

Вы можете воспользоваться *широчайшим набором библиотечных компонентов* не только из стандартной поставки, но и из таких Интернет-порталов, как DigiKey, Mouser, Arrow, RS Components. Полученные компоненты можно установить на схему непосредственно из Интернета, а затем можно скорректировать их и сохранить в единую библиотеку ЭРИ предприятия.

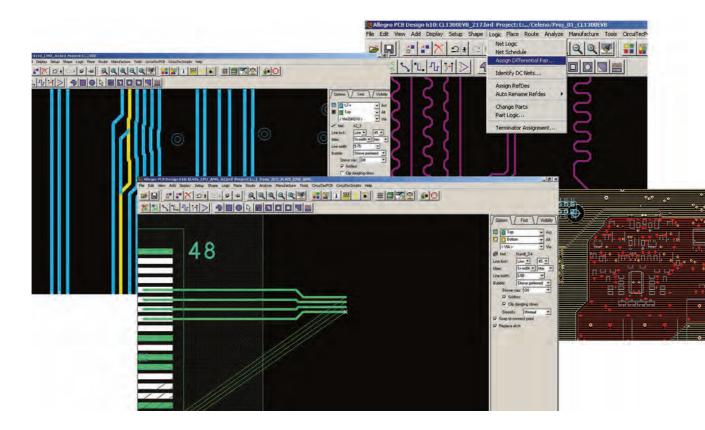

Мощный функционал ручной трассировки позволяет вам мгновенно прокладывать одиночные сигналы, дифф.пары, шины и просто сгруппированные наборы связей. Система *выравнивания длин* сигналов эффективно обеспечивает все современные требования к трассировке скоростных интерфейсов типа PCIe, Ethernet, HDMI, DDR (T-соединения, Fly-By) и др.

Быстрая прокладка шин на плате

3-D вьюер, встроенный в редактор ПП

Полная интеграция с библиотеками компонентов предприятия, PDM-системами (SolidWorks EPDM, Windchill, TeamCenter и др.), с механическими САПР (Компас 3D, SolidWorks, Creo и др.), возможность импорта и экспорта STEP-моделей компонентов, корпуса и печатного узла делают Cadence Allegro идеальным решением для крупных предприятий – разработчиков сложной электроники.

Компания PCB SOFT предлагает также воспользоваться онлайн-библиотекой Ultra Librarian, содержащей 8 млн верифицированных УГО, футпринтов и 3D-моделей. Подписка оформляется на год, после чего регулярно продлевается.

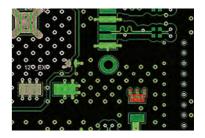

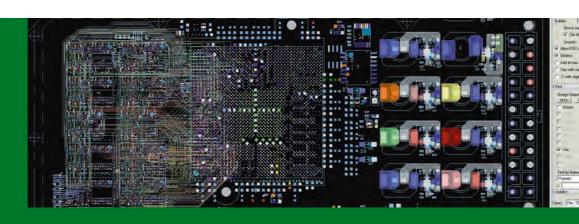

## Конфигурация рабочих мест для проектирования ПП

САПР **Cadence Allegro** поставляется в виде базовой лицензии и набора дополнительных опций, которые являются «надстройкой» над базовой лицензией и обеспечивают более мощный специализированный функционал для различных специализированных применений.

Все лицензии и опции являются плавающими, не привязанными к конкретному рабочему месту, поэтому их могут использовать на конкурентной основе разные сотрудники и отделы предприятия. Для этого в локальной сети предприятия организуется сервер лицензий, в задачи которого входит управление лицензиями.

**Базовая лицензия** Cadence Allegro предназначена для разработки печатных плат высокой сложности, с учетом современных требований по технологичности и целостности сигналов. В нее входят следующие функциональные модули:

- Схемные редакторы Design Capture и Design Authoring

- Редактор условно-графических обозначений и менеджер библиотек

- Редактор печатных плат (PCB Designer)

- Редактор посадочных мест компонентов и падстеков, менеджер библиотек

- Система управления ограничениями и правилами (Constraint Manager)

- Система управления библиотекой компонентов (Component Information System)

- Автотрассировщик Specctra на 6 сигнальных слоев

- Система анализа целостности сигналов SigXplorer

Фирма Cadence предлагает широкий спектр ПО для проектирования плат

#### Опции Cadence Allegro

**Опция High Speed** для работы с высокоскоростными платами. Она добавляет:

- Интерактивно-автоматическое выравнивание длин сигналов (DDR, PCIe и др.)

- Трассировка высокоскоростных цепей под углом к стекловолокну, с выступами, с переходными отверстиями для возвратных токов, и др.

#### **Опция Miniaturization** для работы с платами высокой плотности:

- Поддержка наборов микроотверстий, правила для плат HDI

- Операции для трассировки гибких плат и др.

#### **Опция Analog/RF** для проектирования аналоговых и СВЧ плат:

- Библиотека параметризованных топологических СВЧ-элементов

- Интеграция с пакетами СВЧ-моделирования (ADS) и др.

#### **Опция Team Design** для командной работы над сложными проектами:

- Разбиение проекта между разработчиками на зоны или наборы слоев

- Возможность одновременного группового редактирования платы

#### **Опция Design Planning** для автоматизации трассировки сложных плат:

• Построение плана трассировки и выборочная авто-трассировка по плану

#### Опция FPGA System Planner для повышения эффективности работы с ПЛИС:

• Оптимизация подключения выводов ПЛИС и упрощение трассировки

#### **Опция PCB Routing** для продвинутой трассировки сложных плат.

• Увеличение числа трассировочных слоев до 256, более мощный набор правил.

# Функционал базовой лицензии и дополнительных опций Cadence Allegro

# Функционал базовой лицензии Cadence Allegro

Оформление схем в соответствии с ЕСКД

Возможность задать порядок трассировки выводов в цепи и выравнивать «плечи» цепи позволяет трассировать скоростные интерфейсы

### Схемный редактор Design Capture

Совместимость с распространенным редактором OrCAD

Возможность импорта схем из PCAD, Altium

Возможность вывода документации по ЕСКД

Огромная библиотека стандартных символов (более 44000)

Он-лайн библиотека компонентов (более 2 миллионов)

Он-лайн магазин приложений, IBIS-моделей и библиотек

Просмотр посадочного места компонента в 3D

Печать схем в интеллектуальный PDF с удобной навигацией

Задание и одновременная прокладка групп сигналов

Одновременное подключение шин

Задание «комнат» для дальнейшей трассировки

Автоматизированная прокладка связей на схеме

Мощный язык скриптом Tcl/Tk для написания подпрограмм

Он-лайн проверка DRC, включая пользовательские правила

Обратное и прямое аннотирование (обмен выводов или элементов)

Перекрестная связь с редактором печатных плат

Импорт и экспорт таблиц выводов ПЛИС

Управление «вариантами исполнения»

Удобный механизм визуальной проверки многостраничных схем

#### Система управления библиотекой (Component Information System)

Встроенная в схемный редактор база данных компонентов

Функционал единой базы компонентов предприятия

Интеграция с PDM-системами: SolidWorks EPDM, Windchill, T-Flex, Search и т.д.

Интерфейс к реляционным базам ЭРИ (SQL, MS Access, Excel)

Возможность параметрического поиска нужных компонентов

Управление «применимостью» ЭРИ, контроль доступа к базе

Возможность подключения 3D-моделей и datasheet на ЭРИ

Поиск ЭРИ в каталогах DigiKey, Mouser и др. из редактора схем

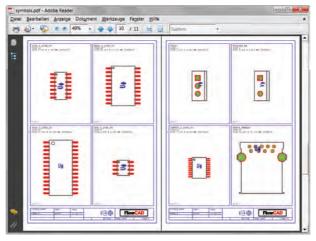

#### Редактор условно-графических обозначений символов (УГО)

Возможность извлечь из схемы и откорректировать символ

Возможность создания УГО из таблицы Excel или datasheet

#### Редактор посадочных мест компонентов

Удобный и мощный «мастер» создания компонентов

Возможность создания площадок произвольной формы

Утилита авто-создания компонентов по IPC-7351

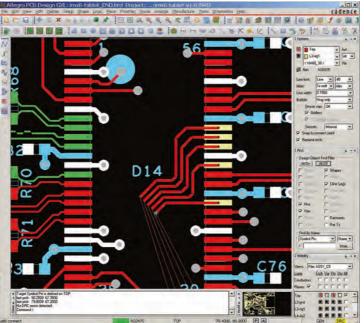

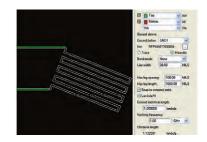

#### Редактор печатных плат (PCB Designer), базовая лицензия

Импорт из PCAD, Altium и других САПР

Импорт конструктива ПП из DXF, IDF или STEP

Редактор стека слоев, калькулятор импеданса

Полупрозрачное отображение слоев

Индикация имени цепи на проводнике, полигоне и выводе

Возможность работы с платой в «зеркальном» отображении

Размещение групп компонентов выбором прямо из схемы

Авто-выравнивание групп компонентов

Полная поддержка трассировки дифференциальных пар

Автоматическое создание «Fan-out»

Автоматическая «доводка» связей

Авто-подрезка, расталкивание, перескок при трассировке

Удобная подсистема прорисовки плана трассировки

Автоматическое создание и авто-выравнивание маркировки

Быстрый экспорт гербер-файлов, DXF и ODB++

Импорт 3D моделей компонентов STEP и IDF

Трассировка группами сигналов

Трассировка Т-разветвлений и Fly-By для DDR

Полуавтоматическое выравнивание длин сигналов DDR и др.

Авто-мультиплицирование фрагментов трассировки

Динамические полигоны с авто-обновлением

«Капельки» на площадках с обеспечением DRC

Авто-размещение массивов переходных отверстий

Создание проектов и спецификаций с «вариантами исполнения»

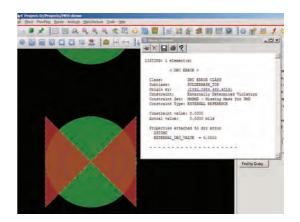

#### Система управления ограничениями и правилами DRC (Constraint Manager)

Физические ограничения DRC (проводники, зазоры, ограничения по длине и др.)

Он-лайн проверки DRC, обеспечение выполнения правил

Возможность подсветки нарушений DRC

Возможность задания правил и ограничений в регионах

Правила проектирования «для производства» (DFM, DFA)

Проверка DRC по высоте компонентов, радиаторов и корпуса

Возможность задать мин. и макс. длину цепи

Ограничение макс. количества переходных отверстий цепи

Продвинутые проверки DRC, такие как «оголенная медь» итд.

#### Автотрассировщик Specctra

Трассировка одновременно в 6 слоях МПП

Полный учет заданных правил и ограничений DRC

Индикация имени цепи на трассах, выводах и полигонах повышает скорость работы

Интерактивная связь между редакторами схем и печатных плат

#### Функционал дополнительных опций CAПР Cadence Allegro

#### Опция High Speed для трассировки высокоскоростных плат

Электрические правила и ограничения

(ECSet – отражения, задержки, перекрестные помехи)

Учет задержек в переходных отверстиях (в 17.2 перенесено в Base)

Учет разбега задержек внутри микросхем (в 17.2 перенесено в Base)

Динамическое выравнивание фазы дифф.пары (в 17.2 перенесено в Base)

Полуавтоматическое выравнивание длины шин DDR

Авто-размещение групп отверстий вдоль трасс

Авто-расталкивание параллельных трасс

Авто-контроль прорезей в полигонах для возвратных токов

Обратная сверловка (в 17.2 перенесено в Base)

#### Опция Miniaturization для плат высокой плотности

Встроенные компоненты в слоях

Наборы микроотверстий

#### Опция Analog/RF для СВЧ плат и аналоговых плат

Продвинутая система установки массивов отверстий

Обширная библиотека СВЧ-элементов топологии

#### Опция Team Design для командной работы над проектом

Разделение печатной платы на зоны по слоям

Разделение печатной платы на зоны по областям

Групповая трассировка печатной платы

Удобная панель управления проектом

Мягкие границы между зонами

Управление классами цепей в зонах

Plated Through-holes (PTH)

Trace

Поддержка современных

любых проектов

технологий, таких как BackDrilling, дает разработчику уникальный

инструмент для эффективного и качественного выполнения

Trace

Stub

Уникальная по удобству работа с полигонами

#### Опция Design Planning для авто-интерактивной трассировки

Возможность анализа осуществимости трассировки

Прорисовка топологического плана трассировки

Авто-генерация топологии проводников по плану

#### Опция FPGA System Planner для трассировки ПЛИС

Учет логических, электрических и физических ограничений

Авто-подбор и оптимальный обмен выводов ПЛИС

Авто-генерация символов УГО для ПЛИС

Минимизация пересечений сигналов при трассировке

#### Опция PCB Routing для продвинутой трассировки

Увеличение числа одновременно доступных слоев до 256

Дополнительные правила для трассировки плат HDI

Продвинутые возможности (встроенные компоненты и др.)

# Опция трассировки Скоростных плат – High Speed Option

Опция Allegro High Speed Option содержит все необходимые дополнительные функции для трассировки высокоскоростных цифровых печатных плат.

Для проектов с частотами сигналов выше 300 МГц (содержащих интерфейсы PCI Express, DDR2/3/4, GHz Ethernet, GTX и др.) крайне важно учитывать все факторы, влияющие на качество сигнала на печатной плате. Конструктору печатной платы нужен инструмент, который не только позволит эффективно выравнивать длины групп сигналов на плате, но и:

- использовать формулы для задания правил выравнивания по длине

- динамически выравнивать фазу сигнала по всей цепи для снижения искажений

- учитывать задержку распространения по оси Z в переходных отверстиях, повышая точность выравнивания

- учитывать разные задержки сигналов внутри микросхем

- обнаруживать некорректное прохождение сигнала над вырезами в полигоне

- распределять трассы по плате для снижения *crosstalk*

**Автоматическое выравнивание задержек.** Allegro теперь более быстро и качественно автоматически выполняет выравнивание задержек. Эта функция чрезвычайно полезна, т.к. количество линий на печатной плате, требующих выравнивания длины, растет и может уже составлять на типовой многослойной плате от нескольких десятков до нескольких сотен штук. Редактор автоматически выравнивает длину выбранных интерактивно трасс в соответствии с заданными правилами.

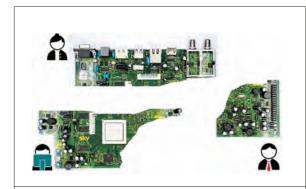

**Смещенная трассировка.** Это весьма актуальная функция для сигналов частотой выше 2 ГГц. Это позволяет за счет трассировки под неортогональным углом усреднить влияние структуры диэлектрика на качество сигнала.

**Динамический контроль фазы сигнала.** Allegro позволяет динамически выравнивать фазу сигнала по всей длине цепи, что крайне важно для снижения искажений. Причем редактор позволяет выделить именно тот фрагмент трассы, на котором произошло рассогласование фазы, и выравнивать фазу локально.

**Учет задержки распространения в переходных отверстиях.** Редактор учитывает задержку распространения по оси Z, в переходных отверстиях, повышая точность выравнивания задержки распространения сигналов.

**Учет разной задержки сигналов внутри микросхем.** САПР учитывает разные задержки сигналов внутри микросхемы, повышая точность выравнивания длин. Задержки внутри микросхемы могут быть заданы в табличном виде или импортированы из текстового файла.

**Поиск вырезов в полигонах.** САПР обнаруживает некорректное прохождение сигнала над вырезами в полигоне (что может служить причиной искажений сигнала).

**Равномерное распределение трасс.** Allegro может автоматически распределять сегменты трасс равномерно, чтобы уменьшить перекрестные помехи от «соседей».

**Обратная сверловка.** САПР поддерживает технологию обратной сверловки для улучшения качества скоростных сигналов.

Полуавтоматическое выравнивание шин DDR существенно ускоряет работу

Учет задержек в переходных отверстиях повышает точность выравнивания сигналов

Автоматическое распределение трасс снижает перекрестные помехи

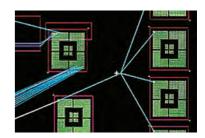

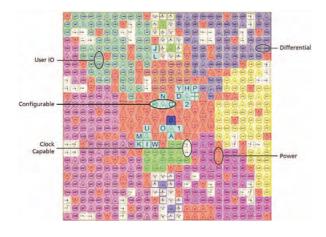

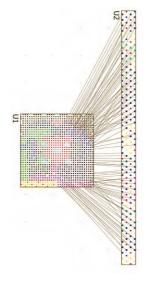

## Опция оптимизации выводов ПЛИС – FPGA System Planner

Подсистема планирования трассировки ПЛИС позволяет конструктору существенно сократить сроки разработки

В ПЛИС задаются группы эквивалентных выводов и банков

# Планировщик ПЛИС автоматизирует все сложные процессы и значительно упрощает и ускоряет разработку печатных плат.

Конструирование печатной платы на ПЛИС, имеющих более 2000 контактов ввода-вывода, для выполнения вручную является слишком сложным. Для завершения проекта на ПЛИС требуется постоянное общение между разработчиками логики, разработчиками системы и разработчиками платы. В целом, это общение является рутинным и даже избыточным. И именно ПЛИС, вследствие огромного числа многомерных правил ввода-вывода, делают процесс общения таким сложным. Эти проблемы могут быть решены за счет применения планировщика ПЛИС, автоматизирующего все эти сложные процессы. В результате, разработка печатных плат для ПЛИС значительно упрощается и ускоряется.

Планировщик ПЛИС полностью автоматизирует процессы связывания контактов ПЛИС с другими компонентами, генерации схем и разводки межсоединений, при этом для всех этих процессов соблюдаются следующие ограничения:

- Логические ограничения разводка контактов должна удовлетворять требованиям протокола соответствующего интерфейса. Например, для шин, синхронных с источником, для успешного захвата данных требуется, чтобы и данные, и соответствующие сигналы синхронизации были правильно выведены на контакты.

- Электрические ограничения связаны с DRC ввода-вывода ПЛИС. ПЛИС имеют сложную структуру банков и детализированный набор соответствующих правил. Для того, чтобы банк стало возможно использовать для интерфейса, должны быть заданы стандартные электрические сигналы этого интерфейса.

- Физические ограничения, связанные с расположением на плате различных устройств. Контакты должны быть выбраны так, чтобы свести к минимуму пересечения проводников и число слоев, требуемых для разводки платы.

#### Функционал опции FPGA System Planner

Учет логических, электрических и физических ограничений

Авто-подбор и оптимальный обмен выводов ПЛИС

Авто-генерация символов УГО для ПЛИС

Минимизация пересечений сигналов при трассировке

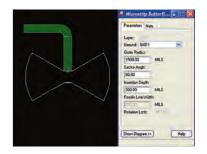

# Опция проектирования СВЧ-плат – *Analog/RF Option*

Опция Analog/RF предоставляет мощный и гибкий набор инструментов для ручного и автоматического размещения, трассировки, и редактирования СВЧ-топологии на печатных платах, как дополнение, встраиваемое в стандартный редактор Allegro PCB Editor.

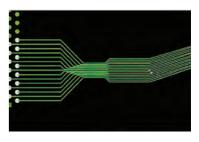

Так как опция Analog/RF поддерживает параметризованные топологические СВЧ-элементы, она предоставляет очень простой механизм для создания, размещения и соединения СВЧ-элементов на плате. Она позволяет легко трассировать полосковые и микрополосковые линии с различными вариантами поворотов, такими как «оптимально скошенный» СВЧ-поворот, скругленный или прямоугольный поворот. Также она позволяет напрямую соединить две точки СВЧ-трассой или меандром. Другие функции для трассировки СВЧ-плат вклютилог.

- Перемещение, поворот, отражение, копирование выбранных СВЧкомпонентов или групп объектов (полигоны, линии, топологические элементы, переходные отверстия)

- Групповое копирование, отражение, вращение СВЧ-компонентов или наборов

- Перенос СВЧ-компонентов или их групп со слоя на слой

- Изменение СВЧ-параметров объектов и автоматическая регенерация их формы в соответствии с новыми параметрами

- Вставка библиотечных СВЧ-компонентов во время трассировки

- Электрические вычисления и индикация параметров СВЧ-трассы

- Создание собственных топологических СВЧ-элементов

- Конвертация СВЧ-элементов в полигоны

- Конвертация трасс редактора Allegro (проводников) в полосковые линии передачи

- Срезание фаски на углах СВЧ-трасс

- Индикация и модификация значений переменных и выражений

- Быстрое размножение СВЧ-фрагментов, включая зеркальное отражение для симметричных/балансных цепей

Вставка RF-элемента при трассировке

Соединение с заданной электрической длиной

Копирование RF-элементов с масштабным множителем

## Новые возможности версии Cadence Allegro 17.2-2016

В мае 2016 года вышла новая версия САПР OrCAD/Allegro – 17.2. С выходом этой версии разработчики получили еще более мощный и эффективный инструмент для проектирования сложнейших печатных плат.

Улучшен графический интерфейс, существенно повысилась скорость выполнения основных операций, добавлено много новых важных функций, связанных с проектированием гибко-жестких плат, командной работой, разработкой высокоскоростных плат, вопросов интеграции с САПР анализа целостности сигналов и 3D-моделирования.

#### Среди новых возможностей САПР Allegro 17.2:

Полноценная работа с дугами упрощает трассировку и коррекции дизайна

- 12 НОВЫХ ПОДКЛАССОВ

- 19 новых вариантов покрытий

- Не требуются визуальные проверки проекта

- Снижается риск ошибок в изготовленных образцах плат

# Уникальные функции для разработки гибко-жестких плат

| Zone 1 Zone 2 Zone 3 Zone 4 Zone 5 | Стек слоев по зонам                                                           |

|------------------------------------|-------------------------------------------------------------------------------|

|                                    | Пример гибко-жесткой платы<br>(фото Sierra Circuits)                          |

|                                    | Правила DRC между слоями<br>ГЖПП сокращают время на<br>ручные проверки        |

|                                    | Полноценная работа<br>с дугами упрощает<br>трассировку и коррекции<br>дизайна |

#### НОВШЕСТВА В РАБОТЕ СО СКОРОСТНЫМИ ПЛАТАМИ

#### Новая опция командной работы

#### Не требуется настройки проекта

- первый разработчик открывает проект, остальные подсоединяются к его компьютеру

- до 5 разработчиков в пределах одной сети

- сокращение времени трассировки до 80% для сложных проектов

- разработчики внутри отдела могут оптимизировать совместную работу, занимаясь большим количеством проектов одновременно и устраняя паузы в работе.

# Сокращение общего времени разработки до 48% (при совместной работе 5 инженеров)

**Было:** асинхронное командное проектирование с разделением проекта на части

**Стало:** синхронная командная работа над одним проектом в сети

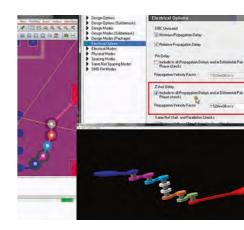

# Интеграция САПР и системы анализа целостности питаний

**Было:** раздельное проектирование в САПР и верификация в системе моделирования – проблемы с настройкой, конвертацией, внесением изменений

**Стало:** совместная настройка САПР и системы моделирования целостности питаний, совместный дизайн и верификация проекта.

#### НОВАЯ РЕАЛИЗАЦИЯ РЕДАКТОРА 3D (QIR3)

#### Было

#### Стало:

- Улучшенная 3D-визуализация

- Связь между 2D и 3D редакторами

- Обнаружение коллизий в 3D

- Устраняет необходимость постоянного обмена с механическим 3D САПР

#### Важные изменения в OrCAD/Allegro

- Поддержка 64-битных ОС.

- Поддержка почти неограниченного объема оперативной памяти

- Допустимый размер файла проекта до 3 ГБ.

- Полное использование мощности многоядерных ЦПУ

- Новый удобный редактор структуры слоев: поддержка многочисленных неэлектрических слоев

- Новый расширенный редактор площадок: поддержка всевозможных форм выводов

- Добавлен импорт схем и печатных плат из Altium

#### ПЕРЕНОС ФУНКЦИЙ ИЗ СТАРШИХ ЛИЦЕНЗИЙ В МЛАДШИЕ

#### Перенесено из Allegro High Speed в Allegro PCB Designer Base:

- Dynamic Differential Pair Phase control

- Pin Delay

- Z-axis delay

- Backdrill

#### Перенесено из Allegro в OrCAD PCB Designer Professional:

- Via2via Line Fattening (HDI),

- Display Segments Over Voids,

- Layer Set Based Routing,

- Diff Pair Routing and DRC,

- Full Xnet Support,

- · Gloss Commands,

- · Contour Routing,

# САПР печатных плат OrCAD (основан на технологиях Allegro)

САПР печатных плат OrCAD является оптимальным по стоимости подмножеством Allegro с урезанным набором функций и невозможностью подключения продвинутых опций Allegro. Если вы на начальном этапе приобрели рабочие места OrCAD, в дальнейшем вы имеете возможность приобрести апгрейд до Allegro либо просто докупить дополнительные рабочие места Allegro. По интерфейсу и формату файлов OrCAD и Allegro полностью совместимы.

Решение OrCAD Standard приобретается обычно небольшими коммерческими компаниями, где всего два-три инженера занимаются трассировкой и проекты имеют невысокую сложность. Для более сложных печатных плат с дифференциальными парами, скоростными сигналами и необходимостью выравнивания длины сигналов приобретается одна или несколько лицензий OrCAD Professional. В случае, если предприятие работает со скоростями, существенно превышающими 1 Гбит/с, обычно приобретается одна или несколько базовых лицензий Allegro PCB Designer, а также одна или несколько лицензий High Speed Option, Team Design Option и т.д, позволяющих еще сильнее поднять качество и эффективность разработки сложных проектов.

#### Оптимизированное меню

По мере реализации новых возможностей к современным САПР печатных плат, в меню добавляется все больше новых пунктов. Но расположены ли эти пункты в оптимальных местах? Являются ли они интуитивно понятными и легко ли их найти? В новом релизе меню оптимизировано, основываясь на обратной связи от пользователей, что помогает сделать ваш процесс проектирования более эффективным.

#### Режим редактирования полигонов

В OrCAD добавлен режим Shape Edit, который специальным образом настраивает среду проектирования, чтобы повысить эффективность и удобство редактирования границ полигонов. С этим новым функционалом вы можете легко выполнять такие действия, как:

- плавный сдвиг границы полигона

- добавление узла к контуру полигона

- групповое изменение углов контура полигоны

#### ПРАВИЛА ДЛЯ СКОРОСТНЫХ ЦЕПЕЙ

Новые правила, ограничения и возможности трассировки помогают вам проектировать высокоскоростные платы:

- **Relative Propagation Delay:** Задает требования по задержкам в согласованных группах цепей

- Static Phase Control: Управляет выравниванием длины между двумя цепями в дифференциальной паре

- **Delay Tune:** Интерактивно добавляет или убирает требуемую длину к выбранной трассе

- **Heads-up Displays:** В онлайн-режиме отображает выполнение заданных правил и ограничений при редактировании скоростных цепей

Сдвиг сегмента границы контура полигона. Сегмент выделяется двумя кликами мыши

Полуавтоматическое создание меандра для выравнивания задержек

#### ТРАССИРОВКА ВДОЛЬ КОНТУРА

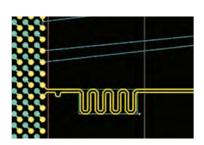

Функция Contour Routing выравнивает трассы вдоль фигурной линии контура во время трассировки (например, в случае трассировки гибких и гибко-жестких плат).

#### ГРУППОВАЯ ТРАССИРОВКА ЦЕПЕЙ

Обновленный функционал Group Route ускоряет прокладку группы трасс за одно движение, с улучшенными возможностями их выбора, он-лайн контролем зазора и вариантами расстановки переходных отверстий.

#### Планирование цепей и ветвления

Функция Net Scheduling позволяет вам задавать определенную последовательность трассировки узлов для цепей, имеющих несколько подсоединений. Точки T-points определяют концы или места ветвлений на протяжении цепи, позволяя каждому сегменту цепи задать именно те правила, которые требуются

#### ТРАССИРОВКА ШТРИХАМИ

Режим трассировки Scribble позволяет вам более упрощенно рисовать путь, которому должна автоматически следовать трассируемая цепь. Он обеспечивает быструю «за два клика» методологию генерации сложных путей для трасс, с применением возможностей протаскивания и расталкивания, и основываясь на ориенгировочном маршруте.

#### Массивы отверстий

Функционал Via Array позволяет вам быстро и легко создавать матрицу или оконтуривание из переходных отверстий, для прошивки полигонов или экранирования вдоль границ трассы. Параметры матрицы могут быть заданы в окне опций, и переходные отверстия добавляются с учетом правил и ограничений DRC.

#### Модули и дополнительные опции OrCAD

Решение OrCAD позволяет подключить дополнительные модули, позволяющие предприятию более эффективно решать те или иные задачи в процессе конструирования печатных узлов.

- OrCAD Lite бесплатный САПР и вьювер схем и печатных плат

- OrCAD Capture схемный редактор

- OrCAD PCB Designer Standard редактор печатных плат

- OrCAD PCB Designer Professional редактор для скоростных и сложных плат

- OrCAD PSpice аналоговое и смешанное моделирование схем

- OrCAD PCB SI анализ целостности сигналов

- OrCAD Library Builder автоматизированное создание библиотек

- OrCAD EDM система управления данными проекта (PDM-система)

- OrCAD Documentation Editor- оформление КД

- OrCAD Panel Editor создание мультиплат

- OrCAD Component Information Portal база данных ЭРИ

- OrCAD DFM Checker технологические проверки

- OrCAD Sigrity ERC электрические проверки

- OrCAD FPGA System Planner оптимизация трассировки выводов ПЛИС

Полуавтоматическая прокладка группы трасс с дугами вдоль указанной линии

Полуавтоматическая прокладка группы цепей и создание группы отверстий

Создание точки разветвлений и указание правил равной длины ветвей

Полуавтоматическая трассировка по указанному направлению (штриху)

Полуавтоматическая расстановка массива отверстий в указанной области

# Продукты OrCAD и Allegro

| Продукты                                  | Описание                                                                                   | Схемный редактор OrCAD Capture |

|-------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------|

| OrCAD Lite                                | Бесплатная версия для просмотра проектов<br>или знакомства с функционалом OrCAD /Allegro   | Ограниченное                   |

| Университетская лицензия                  | Групповые студенческие лицензии<br>по сниженной цене                                       | Да                             |

| OrCAD Capture                             | Популярный в промышленности<br>схемный редактор                                            | Да                             |

| OrCAD PSpice Designer                     | Схемный редактор OrCAD Capture и пакет<br>аналого-цифрового моделирования PSpice A/D       | Да                             |

| OrCAD PSpice Designer Plus                | Пакет для продвинутого аналого-цифрового моделирования и верификации                       | ДА                             |

| OrCAD PCB Designer Standard               | Базовая версия редактора печатных плат OrCAD                                               | Да                             |

| OrCAD PCB Designer Professional           | Редактор печатных плат с продвинутыми возможностями для сложных и скоростных печатных плат | Да                             |

| OrCAD PCB Designer Professional w/ PSpice | Полный пакет САПР печатных плат с возможностью моделирования                               | Да                             |

| OrCAD PCB SI                              | Решение для верификации целостности<br>сигналов на печатной плате                          |                                |

| Allegro PCB Designer                      | Продвинутое решение для крупных предприятий со скоростными печатными платами               | Да дополненный                 |

| Опции Allegro PCB                            |                                                |

|----------------------------------------------|------------------------------------------------|

| Allegro PCB High Speed Option                | Проектирование высокоскоростных плат           |

| Allegro PCB Miniaturization Option           | Проектирование HDI-плат                        |

| Allegro PCB Analog/RF Option                 | Проектирование СВЧ-плат                        |

| Allegro Manufacturing Option                 | Пред-производственная обработка проекта        |

| Allegro PCB Design Planning Option           | Авто-интерактивная трассировка                 |

| Allegro PCB Team Design Option               | Командная работа с трассировкой                |

| Allegro Sigrity SI Base                      | Продвинутое моделирование целостности сигналов |

| Allegro Sigrity PI Base                      | Анализ целостности питаний AC и DC             |

| Allegro FPGA System Planner (2 FPGA, 4 FPGA) | Оптимизация выводов ПЛИС для трассировки       |

| Allegro ASIC Prototyping with FPGA's         | Прототипирование СБИС с помощью ПЛИС           |

| Allegro Design Workbench (Allegro EDM)       | Распределенная работа с единой библиотекой     |

| Allegro AMS Simulator                        | Продвинутое аналоговое моделирование в PSPICE  |

| Allegro PCB Routing Option                   | Продвинутая автотрассировка HDI-плат           |

| База<br>компонентов<br>OrCAD CIS | Аналоговое<br>моделирование<br>PSpice A/D | Продвинутое<br>моделирование PSpice<br>Advanced Analysis | Редактор<br>печатных плат<br>OrCAD PCB Editor | Автотрассиров-<br>щик SPECCTRA<br>for OrCAD | Целостность<br>сигналов OrCAD<br>Signal Integrity |

|----------------------------------|-------------------------------------------|----------------------------------------------------------|-----------------------------------------------|---------------------------------------------|---------------------------------------------------|

| Ограниченное                     | Ограниченное                              | Ограниченное                                             | Ограниченное                                  | Ограниченное                                | Ограниченное                                      |

| Да                               | Да                                        | Да                                                       | Да, продвинутый                               | Да                                          | Да                                                |

| Опция                            |                                           |                                                          |                                               |                                             |                                                   |

| Опция                            | Да                                        | Опция                                                    |                                               |                                             |                                                   |

| Опция                            | Да                                        | ДА                                                       |                                               |                                             |                                                   |

| Опция                            |                                           |                                                          | Да, базовый                                   |                                             |                                                   |

| Опция                            |                                           |                                                          | Да, продвинутый                               | Да                                          | Да                                                |

| Опция                            | Да                                        | Опция                                                    | Да, продвинутый                               | Да                                          | Да                                                |

|                                  |                                           |                                                          |                                               |                                             | Да                                                |

| Да                               | Опция                                     | Опция                                                    | Да дополненный                                | Да продвинутый                              | Да дополненный                                    |

| Дополнительные продукты OrCAD      |                                                          |

|------------------------------------|----------------------------------------------------------|

| OrCAD Library Builder              | Автоматизированное создание библиотек                    |

| OrCAD EDM                          | Система управления данными проекта                       |

| OrCAD Documentation Editor         | Оформление КД                                            |

| OrCAD Panel Editor                 | Создание мультиплат                                      |

| OrCAD Component Information Portal | База данных ЭРИ и доступ к интернет-порталам компонентов |

| OrCAD DFM Checker                  | Технологические проверки                                 |

| OrCAD Sigrity ERC                  | Электрические проверки                                   |

| OrCAD PCB Productivity Toolbox     | Утилиты для ускорения работы                             |

| OrCAD FPGA System Planner          | Назначение выводов ПЛИС                                  |

# Набор функций OrCAD и Allegro

| Размещение и трассировка – PCB EDITOR           Неограниченная база данных         До 1000         Да         да <td< th=""><th>Функции</th><th>OrCAD Lite</th><th>OrCAD<br/>Standard</th><th>OrCAD<br/>Professional</th><th>Allegro</th></td<> | Функции                                         | OrCAD Lite | OrCAD<br>Standard | OrCAD<br>Professional | Allegro |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------|-------------------|-----------------------|---------|

| Связь со схемным редактором         да         <                                                                                                                              | Размещение и трассировка – PCB EDITOR           |            |                   |                       |         |

| Редактор падстеков и футпринтов         да                                                                                                                                    | Неограниченная база данных                      | До 1000    | да                | да                    | да      |

| Визуализация STEP моделей 3D         да                                                                                                                                       | Связь со схемным редактором                     | да         | да                | да                    | да      |

| НАСТРАИВАЕМЫЙ АВТОМАТИЧЕСКИЙ ЧЕРТЕЖ СВЕРЛОВКИ ОТВЕРСТИЯ В ПЛОЩАДКАХ, ГЛУХИЕ И СКРЫТЫЕ ПО Да АВТОРАЗМЕЩЕНИЕ, бЫСТРАЯ РАССТАНОВКА, ПЛАН ОГВЕРСТИЯ В ПЛОЩАДКАХ, ГЛУХИЕ И СКРЫТЫЕ ПО Да АВТОРАЗМЕЩЕНИЕ, бЫСТРАЯ РАССТАНОВКА, ПЛАН ОГРАНИЧЕНО Да АВ Да Д                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Редактор падстеков и футпринтов                 | да         | да                | да                    | да      |

| Отверстия в площадках, глухие и скрытые ПО         да         да         да         да           Авторазмещение, быстрая расстановка, план         ограничено         да                                                                                                                    | Визуализация STEP моделей 3D                    | да         | да                | да                    | да      |

| Авторазмещение, быстрая расстановка, план ограничено да                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Настраиваемый автоматический чертеж сверловки   | ДА         | ДА                | ДА                    | ДА      |

| Динамические полигоны с онлайн-прорисовкой да                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Отверстия в площадках, глухие и скрытые ПО      | да         | да                | да                    | да      |

| Ассоциативные размерные линии да                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Авторазмещение, быстрая расстановка, план       | ограничено | да                | да                    | да      |

| Генерация файлов Gerber 274x, 274D         да                                                                                                                                 | Динамические полигоны с онлайн-прорисовкой      | да         | да                | да                    | да      |

| Импорт и экспорт IPC-2581         да         да <td< td=""><td>Ассоциативные размерные линии</td><td>да</td><td>да</td><td>да</td><td>да</td></td<>                                      | Ассоциативные размерные линии                   | да         | да                | да                    | да      |

| Гипертекстовые отчеты HTML да                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Генерация файлов Gerber 274x, 274D              | да         | да                | да                    | да      |

| DFM DRC (проверки на технологичность)         да                                                                                                                              | Импорт и экспорт IPC-2581                       | да         | да                | да                    | да      |

| Интерактивная трассировка (расталкивание трасс)         ограничено         Да         Да         Да           Автогенерация маркировки         ограничено         Да         Да         Да         Да           Разрезка полигонов         Да         Да <td>Гипертекстовые отчеты HTML</td> <td>да</td> <td>да</td> <td>да</td> <td>да</td>                             | Гипертекстовые отчеты HTML                      | да         | да                | да                    | да      |

| Автогенерация маркировки ограничено да                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DFM DRC (проверки на технологичность)           | да         | да                | да                    | да      |

| Разрезка полигонов       да       Да       да       да         Поддержка макрокоманд, язык SKILL       да       да       да       да         Создание вариантов чертежа / BOM       да       да       да       да       да         Импорт CAПР IFF, PADS®, P-CAD®, Altium®       да       да       да       да       да       да         Импорт-экспорт DXF, IDX, IDF, STEP       да                                                                                                                                                                                                             | Интерактивная трассировка (расталкивание трасс) | ограничено | да                | да                    | да      |

| Поддержка макрокоманд, язык SKILL Да Да Да Да Да Да Создание вариантов чертежа / ВОМ Да Да Да Да Да Да Импорт САПР IFF, PADS®, P-CAD®, Altium® Да Да Да Да Да Да Да Импорт-экспорт DXF, IDX, IDF, STEP Да Да Да Да Да Да Привязка к объектам при трассировке Да Да Да Да Да Да ВРЕдактирование стековых микроотверстий Да Да Да Да Да Да Поддержка перемычек Да Да Да Да Да Да Поддержка перемычек Да Да Да Да Да Да Капельки на концах трасс Да Да Да Да Да Авторазмножение фрагментов Да Да Да Да Да Автовыравнивание компонентов Да Да Да Да Да Интерактивное выравнивание задержек Да Да Да Да Автогенерация тестовых точек Да Да Да Да Констрейны в регионах (ВGА и т.д.) Ограничено Да Д                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Автогенерация маркировки                        | ограничено | да                | да                    | да      |

| Создание вариантов чертежа / ВОМ         да                                                                                                                                   | Разрезка полигонов                              | да         | да                | да                    | да      |

| Импорт САПР IFF, PADS®, P-CAD®, Altium®         да         да <td>Поддержка макрокоманд, язык SKILL</td> <td>да</td> <td>да</td> <td>да</td> <td>да</td>                                 | Поддержка макрокоманд, язык SKILL               | да         | да                | да                    | да      |

| Импорт-экспорт DXF, IDX, IDF, STEP       да                                                                                                                                                                                                                                    | Создание вариантов чертежа / ВОМ                | да         | да                | да                    | да      |

| Привязка к объектам при трассировке  Да                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Импорт САПР IFF, PADS®, P-CAD®, Altium®         | да         | да                | да                    | да      |

| Привязка к объектам при грассировке  Да  Да  Да  Да  Да  Да  Да  Да  Да  Д                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Импорт-экспорт DXF, IDX, IDF, STEP              | да         | да                | да                    | да      |

| Редактирование стековых микроотверстий да                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Привязка к объектам при трассировке             | да         | да                | да                    | да      |

| Поддержка перемычек  Да  Да  Да  Да  Да  Да  Да  Да  Да  Д                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DRC зазор в той же цепи                         | да         | да                | да                    | да      |

| Трассировка штрихами  Да  Да  Да  Да  Да  Да  Да  Да  Да  Д                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Редактирование стековых микроотверстий          | да         | да                | да                    | да      |

| Капельки на концах трасс       да       да       да         Авторазмножение фрагментов       ограничено       да       да         Автовыравнивание компонентов       да       да       да         Объединение и разделение микроотверстий       да       да       да         Интерактивное выравнивание задержек       да       да       да         Автогенерация тестовых точек       да       да       да         Констрейны в регионах (ВGA и т.д.)       ограничено       да       да         Цветовая онлайн-индикация выполнения правил       да       да       да                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Поддержка перемычек                             | да         | да                | да                    | да      |

| Авторазмножение фрагментов ограничено да да да Автовыравнивание компонентов да                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Трассировка штрихами                            | да         | да                | да                    | да      |

| Автовыравнивание компонентов       да       да       да         Объединение и разделение микроотверстий       да       да       да         Интерактивное выравнивание задержек       да       да       да         Автогенерация тестовых точек       да       да       да         Констрейны в регионах (ВGA и т.д.)       ограничено       да       да         Цветовая онлайн-индикация выполнения правил       да       да       да                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Капельки на концах трасс                        | да         |                   | да                    | да      |

| Объединение и разделение микроотверстий       да       да       да         Интерактивное выравнивание задержек       да       да       да         Автогенерация тестовых точек       да       да       да         Констрейны в регионах (ВGA и т.д.)       ограничено       да       да         Цветовая онлайн-индикация выполнения правил       да       да       да                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Авторазмножение фрагментов                      | ограничено |                   | да                    | да      |

| Интерактивное выравнивание задержек       да       да       да         Автогенерация тестовых точек       да       да       да         Констрейны в регионах (ВGA и т.д.)       ограничено       да       да         Цветовая онлайн-индикация выполнения правил       да       да       да                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Автовыравнивание компонентов                    | да         |                   | да                    | да      |

| Автогенерация тестовых точек       да       да       да         Констрейны в регионах (ВGА и т.д.)       ограничено       да       да         Цветовая онлайн-индикация выполнения правил       да       да       да                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Объединение и разделение микроотверстий         | да         |                   | да                    | да      |

| Констрейны в регионах (BGA и т.д.) ограничено да да<br>Цветовая онлайн-индикация выполнения правил да да                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Интерактивное выравнивание задержек             | да         |                   | да                    | да      |

| Цветовая онлайн-индикация выполнения правил да да да                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Автогенерация тестовых точек                    | да         |                   | да                    | да      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Констрейны в регионах (BGA и т.д.)              | ограничено |                   | да                    | да      |